Introduction

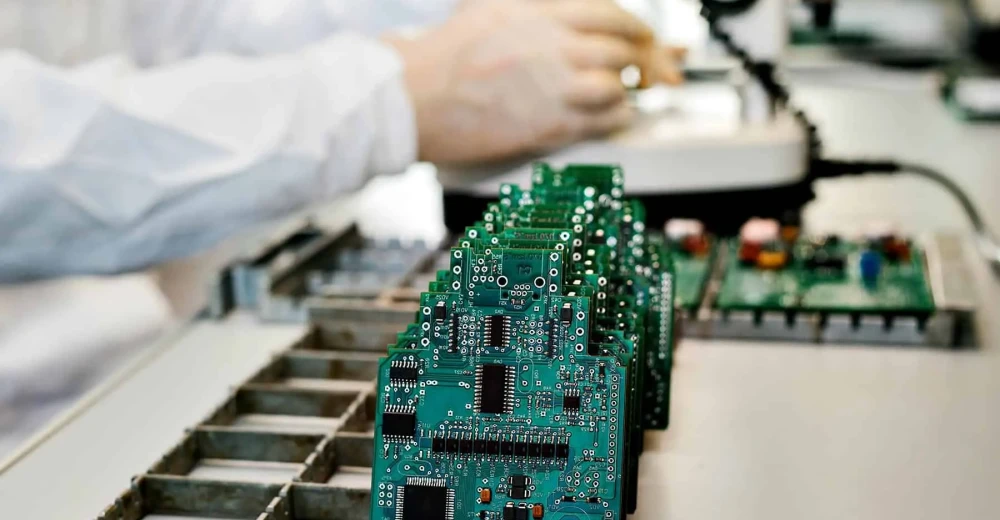

As modern electronics continue to pack more functionality into smaller packages, high density interconnect (HDI) printed circuit boards (PCBs) have become essential for many applications. HDI PCBs allow routing of traces between very closely spaced components, enabling miniaturized and lightweight products.

However, the design rules for HDI are much tighter than for conventional PCBs. Features like traces, spaces, and capture pads need to be specifically optimized for reliability and manufacturability. If not done properly, a board may exhibit problems like opens, shorts, or floating copper that render it unusable.

This article examines feature size requirements and design techniques to ensure your HDI PCB layout satisfies design for manufacturability (DFM) rules. We will cover factors like stackup, trace width/space, capture pads, and via strategies. Following these guidelines allows you to fully utilize HDI technology while avoiding common pitfalls.

HDI Stackup Considerations

A unique aspect of HDI PCBs is the stacked via structure. This refers to using multiple laminated dielectric buildup layers rather than drilling completely through the board. The key advantage is that via holes can be made smaller since they only penetrate the top few layers.

Typical HDI stackups involve alternating core, buildup, and prepreg layers:

- Core – Thick, rigid FR-4 layer that provides mechanical structure

- Buildup – Thin dielectric layer for routing fine lines

- Prepreg – Adhesive used to bond core and buildup layers

The core thickness depends on stiffness requirements. 2-8 mil cores are common. Buildup layers are usually 2-3 mils thick. Typical HDI designs utilize 1-6 buildup layers.

The stackup configuration directly impacts the achievable via size, line widths, and spaces. Thicker dielectric layers allow wider spacing, while thinner buildups enable tight precision. Select your HDI stackup wisely based on the design constraints.

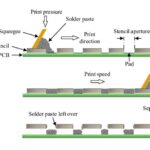

Trace and Space DFM Rules

Traces on HDI layers need to be optimized for precision manufacturing capabilities. Follow these guidelines for trace widths and clearances:

- Minimum trace width: 4 mils

- Minimum trace space: 4 mils

- Preferred trace width: ≥ 6 mils

- Preferred trace space: ≥ 6 mils

Keep traces and spaces above 6 mils when possible. Below 5 mils becomes very challenging to produce. For power traces up to 70 mils can be used.

When traces change layers through a via, strive for 1:1 landing relationships:

This prevents stubs and helps maintain impedance control. Try to avoid teardrops or via caps which can infringe on near- neighbor traces.

Use larger clearances when adjacent to edge board connectors or in high voltage areas. Certain RF circuits require wider transmission lines.

Capture Pad Design

Capture pads connect traces to vias and component pads. The size and shape impacts manufacturability. Use the following capture pad dimensions:

| Layer | Minimum Size | Preferred Size | Shape |

|---|---|---|---|

| Core | 14 mil round | 20+ mil round | Round |

| Buildup | 8 mil round | 12+ mil round | Round |

Larger capture pads are recommended when possible. This provides margin and helps maximize yield.

Always make capture pads round rather than rectangular or oval. The latter can create pointed edges that violate spacing tolerances. Rounded shapes are far more reliable.

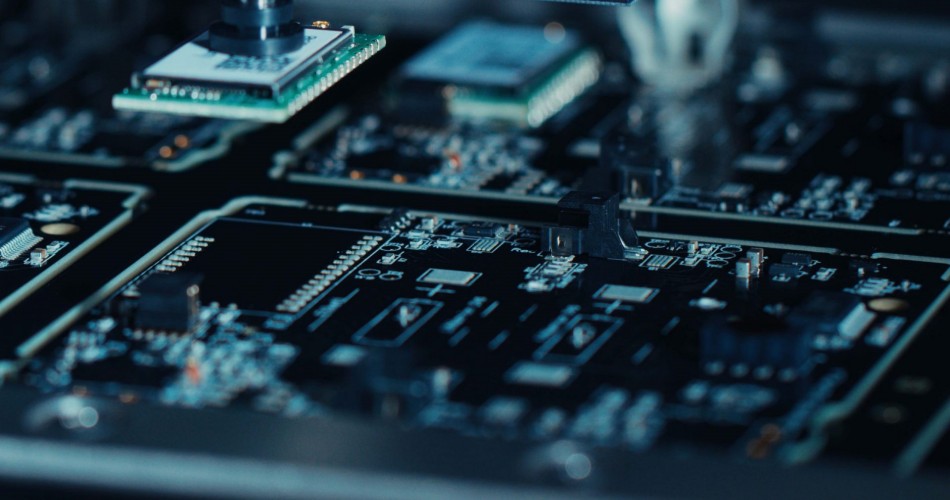

Via Strategies

Creating robust vias in HDI requires managing size, spacing, tenting, and layout:

- Laser Drilled Vias – Small vias are made by sequentially laser drilling each buildup layer. This permits min via holes down to 3-4 mils.

- Stack Vias Intelligently – Place ground/power vias in a row. Signal vias can align orthogonally.

- Use Via Walls Sparingly – Avoid long chains of vias which risk reliability issues.

- Watch Spacing Rules – Adhere to 8 mil center-to-center via spacing for laser drilled vias.

- Tenting Vias – Plug vias on outer layers with soldermask to prevent contamination.

By tailoring vias for HDI you can achieve the interconnection density needed while mitigating potential defects. Consult your board shop on specific requirements.

Component Spacing and Density

With HDI capabilities, components can be assembled very close together. However, certain minimum spacings should still be observed:

- 0201 chip passive spacing: 4 mil chip-to-chip, 6 mil chip-to-trace

- 01005 chip passive spacing: 2 mil chip-to-chip, 4 mil chip-to-trace

- Fine pitch BGA spacing: 6 mil ball-to-ball, 8 mil ball-to-trace

The assembly equipment constrains how densely devices can actually be placed. While HDI routing can escape tightly packed parts, be reasonable about component density to enable fabrication.

Layer Count Optimization

More available routing layers allows greater flexibility to escape dense devices. However balance this with costs, as each additional layer drives up expense.

Evaluate whether a 4-layer, 6-layer, or 8-layer HDI stackup provides the right tradeoff between routability and costs for your design requirements. Adding just 2 extra layers can make routing substantially easier if component density is high.

HDI Design Review Checklist

To ensure your design conforms to HDI DFM principles, use this checklist throughout the layout process:

- Follow stackup guidelines – limit buildup layers and watch dielectric thicknesses

- Use appropriate trace width/space rules – 6/6 mil or above when possible

- Utilize correct capture pad sizes and rounded shapes

- Check via hole sizes and use intelligent stacking patterns

- Adhere to minimum component spacing rules

- Optimize layer count for routability without overdesign

- Review fab shop design rules and perform DRC signoff

Rigorously following these guidelines will help you harness the full potential of HDI for your application needs.

Conclusion

Designing for HDI introduces tighter tolerances versus conventional PCB layout. Features like traces, spaces, capture pads, and vias must be adapted to enable small laser-drilled holes and thin dielectric clearances.

By optimizing your layout for HDI stackups, scaling dimensions appropriately, and stacking vias intelligently, you can achieve the routing density needed for highly compact designs. Balancing component spacing and layer counts is also key.

Work closely with your PCB manufacturer to validate all design rules and manufacturing capabilities. This ensures your board can be fabricated correctly the first time. Following the guidelines described here will set you on the right path to harnessing the benefits of HDI technology.

Frequently Asked Questions

What are some key advantages of HDI PCB technology?

The main benefits of HDI are:

- Increased routing density through finer features and more layers

- Smaller vias by using sequential stacked laser drilling

- Higher speeds from tightly spaced matched impedance lines

- More flexibility for escaping dense fine-pitch components

- Overall miniaturization of products

Can HDI be combined with blind/buried vias?

Yes, blind/buried vias are very commonly used together with stacked HDI microvias. Blind vias only penetrate part of the board while buried vias are completely internal. This allows greater routing density.

What are the main reliability risks to watch for with HDI?

Some potential issues include:

- Fracturing or cracking of thin dielectric layers

- Separation of buildup dielectric from base laminate

- Opens or shorts from reduced spacing tolerances

- Thermal stresses on vias and plated through holes

Proper design and qualification is key to maximizing reliability.

What are typical HDI applications?

HDI is commonly used for products like:

- Smartphones and tablets

- Wearables

- Internet of Things (IoT) devices

- High-speed data communications

- Compact consumer electronics

- Aerospace and defense electronics

Wherever miniaturization, high speeds, or complexity are needed, HDI provides advantages.

Beyond PCBs, what other technologies utilize HDI?

HDI techniques are also widely used in semiconductor wafer fabrication. Stacked vias, thin film dielectrics, and high density interconnects are critical to manufacturing silicon chips. The same principles apply at a very small scale.

Leave a Reply